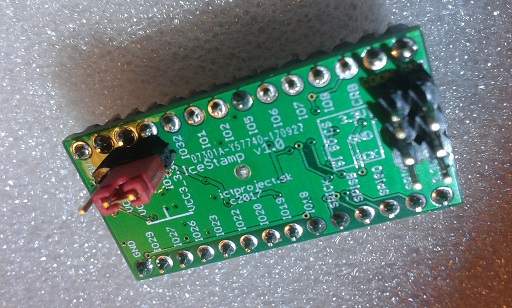

1. built around Lattice ICE40LP384, 384 cells, 21 IOs

2. DIL28 socket, single 3.3V power

3. the FPGA bitstream loads from the on-board flash, or from an MCU, ie. stm32, etc.

4. flash programming for example via the cheapo “usbasp” programmer (modded fw, free), or an FT232H, etc.

5. FPGA development (verilog, vhdl) in Lattice’s IceCube2 or in IceStorm (both free)

- IceStamp_prototype.jpg (91.48 KiB) Viewed 916 times

http://gnarlygrey.atspace.cc/development-platform.html

I’ve purchased 2 of them recently and played a bit with it.

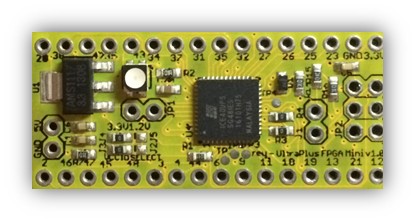

5.3K LUTs, 1Mb SPRAM, 120Kb DPRAM, 8 Multipliers ?

That is ways better than the 384 cells of the other board.

5.3K LUTs could even be sufficient for a small MC, I think.

Lattice supplied the chips, I would guess

The UPduino board is of great size – DIL32, interestingly the pcb is almost transparent (as it lacks any solid ground plane, not easy to do in such format with only 2 layers). SPI flash and a voltage regulator at the bottom side. It calls for 4 layers, sure.

These chips are (ultra) low power, but quite fast (40nm technology, the smaller one runs here 320MHz internally) so a good grounding could be necessary..

I’ve been able to port some simple old project done in the past on Altera or Xilinx, a I2C Slave controlling 3 PWM output to the RGB Led, overall using only 10% of the LUT. Considering that this chip has already some HW I2C builtin, which I didn’t use, maybe I should redo the project using them to drop usage below 5%.

@Martin: I’ve been blinded by your RGB demo (from eevblog) running just now in front of me..

Grounding/gnd_planes: is important because of signal integrity issues, quite common with fpga designs.. The IceXX chips support ie LVCMOS 3.3/2.5/1.8/1.2V, diff signalling – LVDS25E, subLVDS with input speeds~500Mbit/s. Thus the signal integrity is important.

[Rick Kimball – Wed Nov 08, 2017 3:32 pm] –

@martinayotte have you tried out LatticeMico32 on that board? If so, how much of the chip does it use?

I know a bit about LatticeMico32 as I’ve look at while ago to see if it could be ported to Xilinx or Altera.

I’m really not sure how much LUTs it will take and if it will even fit in those tiny UPDuino …

I’m busy these days, but maybe I will try when I will get a chance !

[Pito – Wed Nov 08, 2017 3:58 pm] –

@Martin: I’ve been blinded by your RGB demo (from eevblog) running just now in front of me..

The RGB demo I’ve posted on EEVBlog is only gnarlygrey example modified to have a FSM with 8 colors, it has nothing with the one I’ve mentioned above with 3x 8bits PWM controlled by I2C slave, which can then fadein/fadeout over million of colors … ![]()

Logic Resource Utilization:

---------------------------

Total Logic Cells: 2249/5280

Combinational Logic Cells: 1558 out of 5280 29.5076%

Sequential Logic Cells: 691 out of 5280 13.0871%

Logic Tiles: 349 out of 660 52.8788%

Registers:

Logic Registers: 691 out of 5280 13.0871%

IO Registers: 0 out of 480 0

Block RAMs: 16 out of 30 53.3333%[Pito – Fri Nov 10, 2017 10:37 pm] –

The Zylin’s ZPU example (but with ~half bram size than the HX8K set in source, needs some fine tuning) fits easily into UPduino

That looks interesting however it seems like development on it has stalled. Is there someplace that talks about that softcore. Everything I found seems to have cooled off in 2015.

Especially that I have already played with original AlvieBoy’s ZPUino on Xilinx.

I think that is the tendency nowadays. You can hardly design a better performing sw MCU inside any fpga than are the cheapest hw off-the-shelf offerings today. The designs are therefore either retro computing exercises, or more-less for educational purposes. If you need a sw MCU within your fpga design all those are considered mature. The fpga vendors published their soft MCUs 10y back in average. Moreover, as an improvement, they started to place hw MCUs inside their fpga fabric..

[martinayotte – Tue Oct 24, 2017 3:40 pm] –

There is also this one :

Mine just showed up in a plain white envelope .. You can see the holes in the plastic bag where the mail sorter machinary squished it .. * crosses fingers and solders on the pins : )

both appear ok.

rather prompt as i was expecting aliexpress travel rates.

srp

Device Utilization Summary

LogicCells : 1153/5280

PLBs : 220/660

BRAMs : 16/30

IOs and GBIOs : 24/36

PLLs : 1/1

http://mecrisp.sourceforge.net/

Mecrisp-Ice 1.0

here . 5892 ok.

ok.

unused . 6396 ok.

ok.

words FACS FAC .FAC SETUP *BUFF LAST F-BUFF MAX-DIGITS save new cornerstone save erase spiwe waitspi random

randombit delay ticks now leds ms endcase endof of case s" within pad unused ." mod / /mod move u.r .r d.r rtype u. . d.

ud. (d.) #> #s # sign hold <# hld BUF BUF0 spaces */ */mod fm/mod sm/rem sgn constant variable m* >body create repeat

while else <= >= u<= u>= ( [char] ['] eint? dint eint load spi> >spi spix idle xor! bic! bis! quit evaluate refill accept number

\ char ' postpone literal abort rdrop r@ r> >r hex binary decimal unloop j i +loop loop ?do leave do recurse does> until again

begin then if ahead ; exit :noname : ] [ immediate foldable sliteral s, compile, c, , allot parse parse-name source 2! 2@

cmove> cmove fill sfind align aligned words here tib init forth >in base state /string type count .x .x2 bl cr space c! c@ emit

key key? emit? um/mod * um* d2* d0= m+ s>d dabs d- dnegate d+ depth io@ io! nip over dup swap u< < = invert not or and

xor - + ! 2/ 2* cells abs bounds umax umin max min 2over 2swap +! 2dup ?dup 2drop tuck -rot rot true false drop u> 0> 0<

> 0<> <> cell+ 0= rdepth @ 1- negate 1+ arshift rshift lshift execute ok.

ok.

300 FAC .FAC 306,057,512,216,440,636,035,370,461,297,268,629,388,588,804,173,576,999,416,776,741,259,476,533,176,716,

867,465,515,291,422,477,573,349,939,147,888,701,726,368,864,263,907,759,003,154,226,842,927,906,974,559,841,225,

476,930,271,954,604,008,012,215,776,252,176,854,255,965,356,903,506,788,725,264,321,896,264,299,365,204,576,448,

830,388,909,753,943,489,625,436,053,225,980,776,521,270,822,437,639,449,120,128,678,675,368,305,712,293,681,943,

649,956,460,498,166,450,227,716,500,185,176,546,469,340,112,226,034,729,724,066,333,258,583,506,870,150,169,794,

168,850,353,752,137,554,910,289,126,407,157,154,830,282,284,937,952,636,580,145,235,233,156,936,482,233,436,799,

254,594,095,276,820,608,062,232,812,387,383,880,817,049,600,000,000,000,000,000,000,000,000,000,000,000,000,000,

000,000,000,000,000,000,000,000,000,000,000 ok.